# M58LW032D

# 32 Mbit (4Mb x8, 2Mb x16, Uniform Block) 3V Supply Flash Memory

# **FEATURES SUMMARY**

- WIDE x8 or x16 DATA BUS for HIGH BANDWIDTH

- SUPPLY VOLTAGE

- V<sub>DD</sub> = V<sub>DDQ</sub> = 2.7 to 3.6V for Program, Erase and Read operations

- ACCESS TIME

- Random Read 90ns,110ns

- Page Mode Read 90ns/25ns, 110ns/25ns

- PROGRAMMING TIME

- 16 Word Write Buffer

- 12µs Word effective programming time

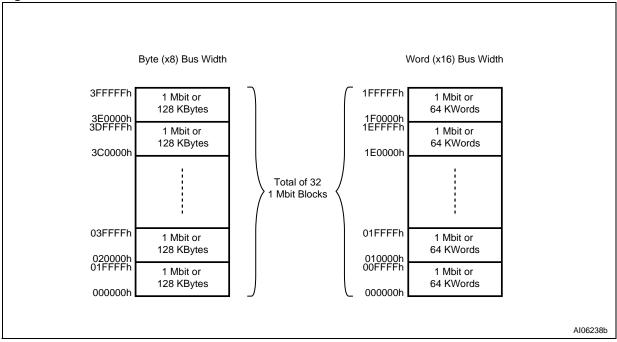

- 32 UNIFORM 64 KWord/128KByte MEMORY BLOCKS

- ENHANCED SECURITY

- Block Protection/ Unprotection

- V<sub>PEN</sub> signal for Program Erase Enable

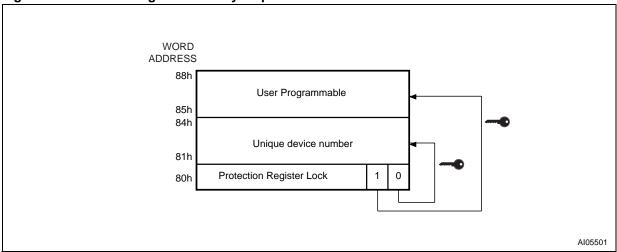

- 128 bit Protection Register with 64 bit Unique Code in OTP area

- PROGRAM and ERASE SUSPEND

- 128 bit PROTECTION REGISTER

- **COMMON FLASH INTERFACE**

- 100, 000 PROGRAM/ERASE CYCLES per BLOCK

- **ELECTRONIC SIGNATURE**

- Manufacturer Code: 0020h

- Device Code M58LW032D: 0016h

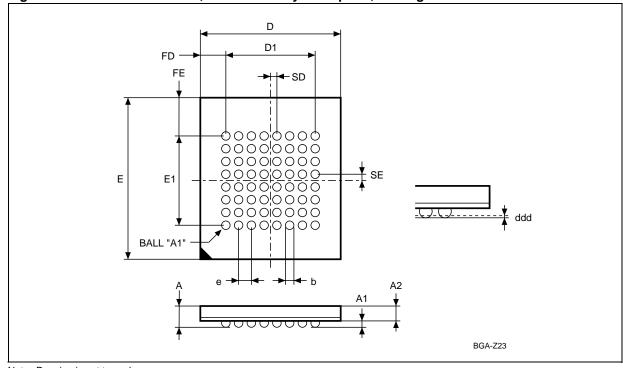

Figure 1. Packages

<u>September 2003</u> 1/51

# M58LW032D

# **TABLE OF CONTENTS**

| SUMMARY DESCRIPTION                                     | 5   |

|---------------------------------------------------------|-----|

| Figure 2. Logic Diagram                                 | 6   |

| Table 1. Signal Names                                   |     |

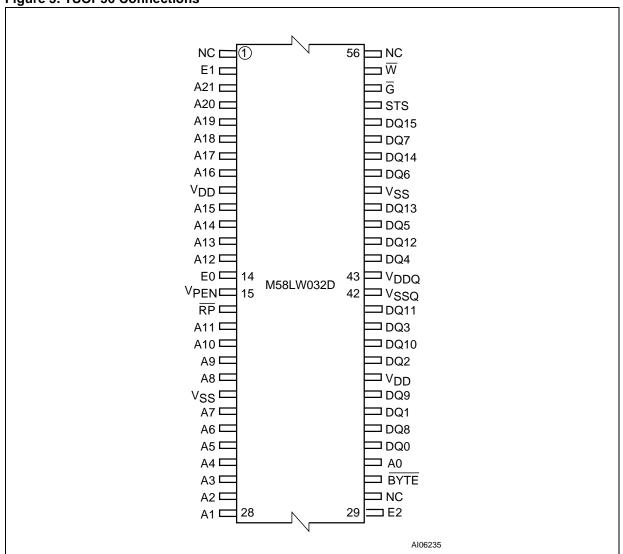

| Figure 3. TSOP56 Connections                            |     |

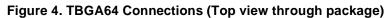

| Figure 4. TBGA64 Connections (Top view through package) |     |

| Figure 5. Block Addresses                               |     |

|                                                         |     |

| SIGNAL DESCRIPTIONS                                     | 10  |

| Address Input (A0)                                      | 10  |

| Address Inputs (A1-A21)                                 | 10  |

| Data Inputs/Outputs (DQ0-DQ15)                          | 10  |

| Chip Enables (E0, E1, E2)                               | 10  |

| Output Enable (G)                                       | 10  |

| Write Enable (W)                                        | 10  |

| Reset/Power-Down (RP)                                   | 10  |

| Byte/Word Organization Select (BYTE)                    | 10  |

| Status/(Ready/Busy) (STS)                               | 10  |

| Program/Erase Enable (V <sub>PEN</sub> )                | 11  |

| V <sub>DD</sub> Supply Voltage                          | 11  |

| V <sub>DDQ</sub> Supply Voltage                         |     |

| V <sub>SS</sub> Ground                                  |     |

| V <sub>SSQ</sub> Ground                                 |     |

| Table 2. Device Enable                                  | 11  |

| BUS OPERATIONS                                          | 12  |

| Bus Read                                                |     |

| Bus Read                                                |     |

| Bus Write                                               |     |

| Output Disable                                          |     |

| Power-Down                                              |     |

| Standby                                                 |     |

| Table 3. Bus Operations                                 |     |

| Table 3. Bus Operations                                 |     |

| READ MODES                                              | 13  |

| OOMMAND INTEREACE                                       | 4.4 |

| COMMAND INTERFACE                                       |     |

| Read Memory Array Command                               |     |

| Read Electronic Signature Command                       |     |

| Read Query Command                                      |     |

| Read Status Register Command                            |     |

| Clear Status Register Command                           |     |

| Block Erase Command                                     |     |

| Word/Byte Program Command                               |     |

| Write to Buffer and Program Command                     | 15  |

|    | Program/Erase Suspend Command                                    | 15   |

|----|------------------------------------------------------------------|------|

|    | Program/Erase Resume Command                                     | 15   |

|    | Block Protect Command                                            | 15   |

|    | Blocks Unprotect Command                                         | 16   |

|    | Protection Register Program Command                              | 16   |

|    | Configure STS Command                                            | . 16 |

|    | Table 4. Commands                                                | 17   |

|    | Table 5. Configuration Codes                                     | 17   |

|    | Table 6. Read Electronic Signature                               | 18   |

|    | Figure 6. Protection Register Memory Map                         | 18   |

|    | Table 7. Word-Wide Read Protection Register                      | 18   |

|    | Table 8. Byte-Wide Read Protection Register                      | 19   |

|    | Table 9. Program, Erase Times and Program Erase Endurance Cycles | 20   |

|    |                                                                  |      |

| ST | ATUS REGISTER                                                    | 21   |

|    | Program/Erase Controller Status (SR7)                            | 21   |

|    | Erase Suspend Status (SR6)                                       | 21   |

|    | Erase Status (SR5)                                               | 21   |

|    | Program Status (SR4)                                             | 21   |

|    | VPEN Status (SR3)                                                | 22   |

|    | Program Suspend Status (SR2)                                     | 22   |

|    | Block Protection Status (SR1)                                    | 22   |

|    | Reserved (SR0)                                                   | 22   |

|    | Table 10. Status Register Bits                                   | 23   |

|    |                                                                  |      |

| MA | XIMUM RATING                                                     | 24   |

|    | Table 11. Absolute Maximum Ratings                               | 24   |

|    |                                                                  |      |

| DC | and AC PARAMETERS                                                | 25   |

|    | Table 12. Operating and AC Measurement Conditions                | 25   |

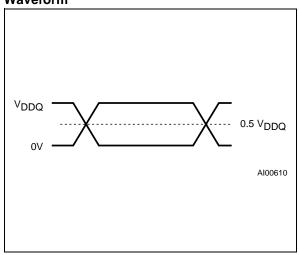

|    | Figure 7. AC Measurement Input Output Waveform                   | 25   |

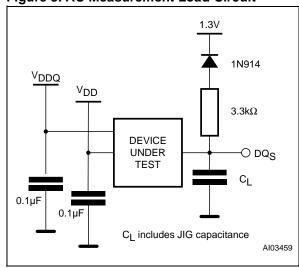

|    | Figure 8. AC Measurement Load Circuit                            | 25   |

|    | Table 13. Capacitance                                            | 25   |

|    | Table 14. DC Characteristics                                     | 26   |

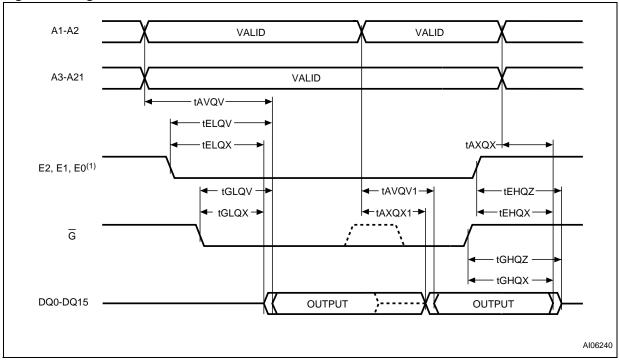

|    | Figure 9. Bus Read AC Waveforms                                  | 27   |

|    | Table 15. Bus Read AC Characteristics                            | 27   |

|    | Figure 10. Page Read AC Waveforms                                | 28   |

|    | Table 16. Page Read AC Characteristics                           | 28   |

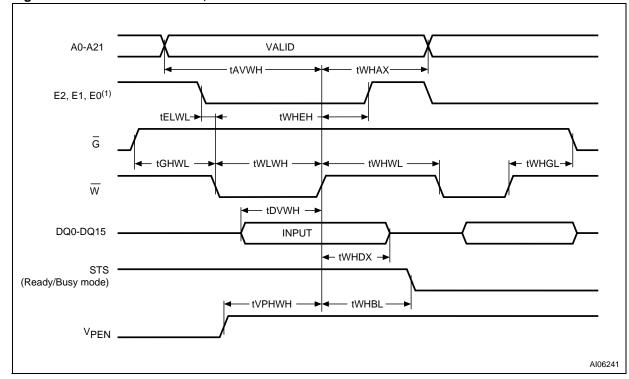

|    | Figure 11. Write AC Waveform, Write Enable Controlled            | 29   |

|    | Table 17. Write AC Characteristics, Write Enable Controlled      | 29   |

|    | Figure 12. Write AC Waveforms, Chip Enable Controlled            | 30   |

|    | Table 18. Write AC Characteristics, Chip Enable Controlled       | 30   |

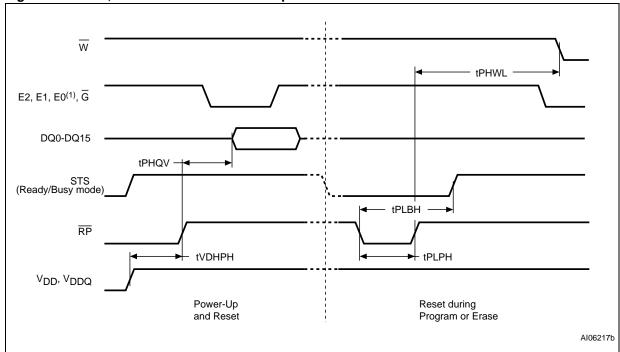

|    | Figure 13. Reset, Power-Down and Power-Up AC Waveform            | 31   |

|    | Table 19. Reset, Power-Down and Power-Up AC Characteristics      | 31   |

# M58LW032D

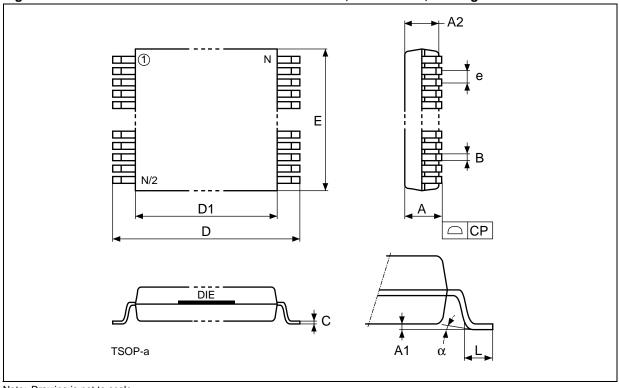

| PACKAGE MECHANICAL                                                                                                                                                             | 32       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 14. TSOP56 - 56 lead Plastic Thin Small Outline, 14 x 20 mm, Package Outline Table 20. TSOP56 - 56 lead Plastic Thin Small Outline, 14 x 20 mm, Package Mechanical Data | 32<br>32 |

| Figure 15. TBGA64 - 10x13mm, 8 x 8 ball array 1mm pitch, Package Outline                                                                                                       | 33<br>33 |

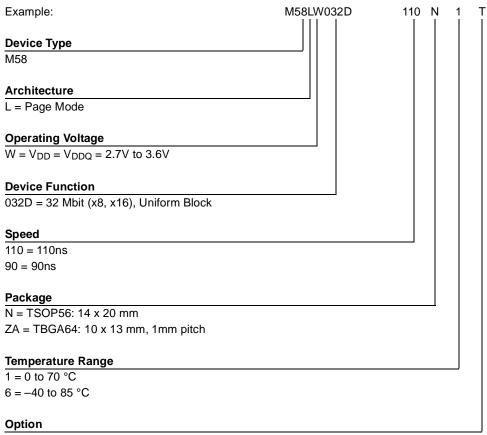

| PART NUMBERING                                                                                                                                                                 | 34       |

| Table 22. Ordering Information Scheme                                                                                                                                          | 34       |

| APPENDIX A. BLOCK ADDRESS TABLE                                                                                                                                                | 35       |

| Table 23. Block Addresses                                                                                                                                                      | 35       |

| APPENDIX B. COMMON FLASH INTERFACE - CFI                                                                                                                                       | 36       |

| Table 24. Query Structure Overview                                                                                                                                             | 36       |

| Table 25. CFI - Query Address and Data Output                                                                                                                                  |          |

| Table 26. CFI - Device Voltage and Timing Specification                                                                                                                        | 37       |

| Table 27. Device Geometry Definition                                                                                                                                           | 37       |

| Table 28. Block Status Register                                                                                                                                                | 38       |

| Table 29. Extended Query information                                                                                                                                           | 39       |

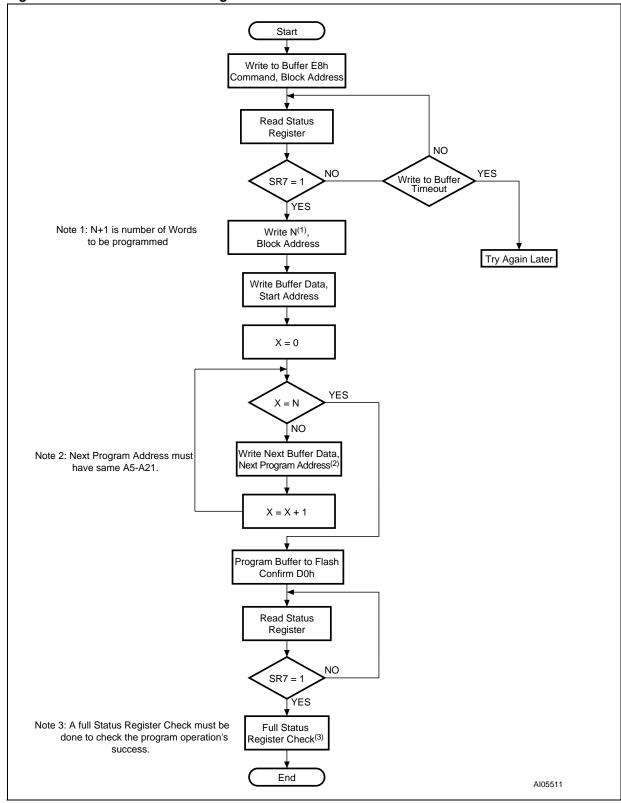

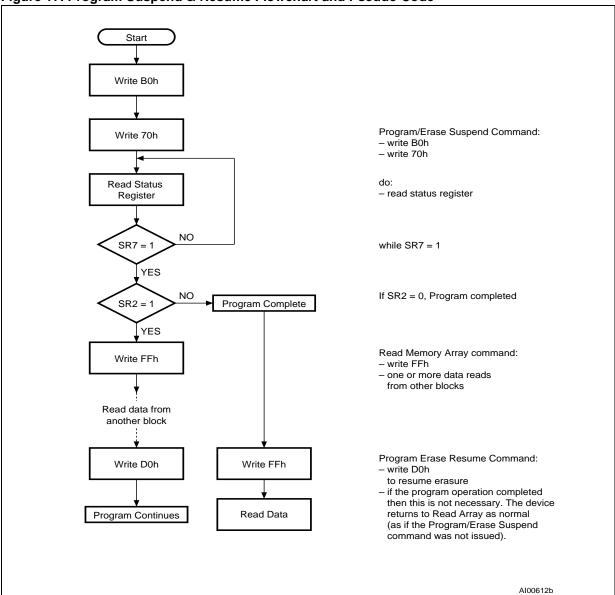

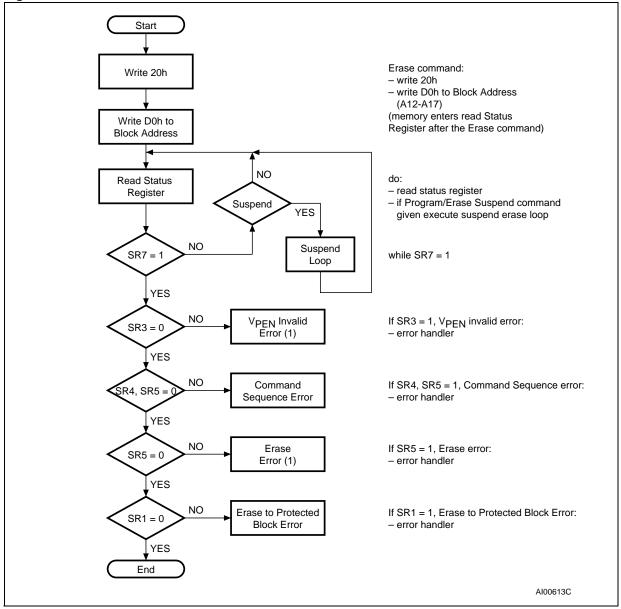

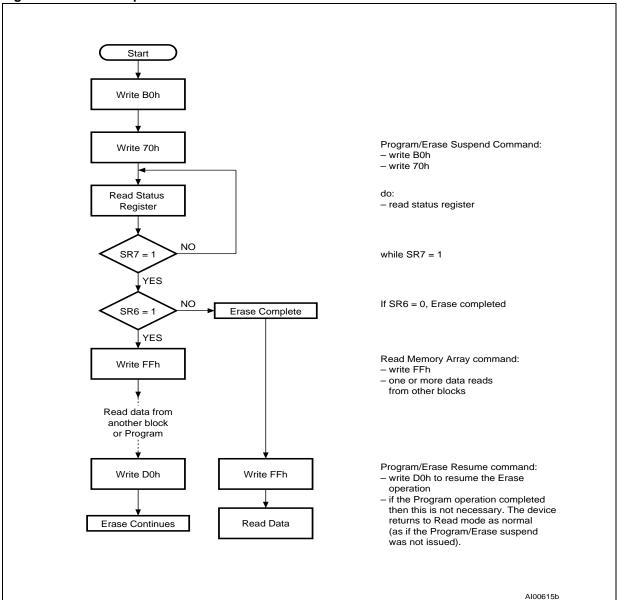

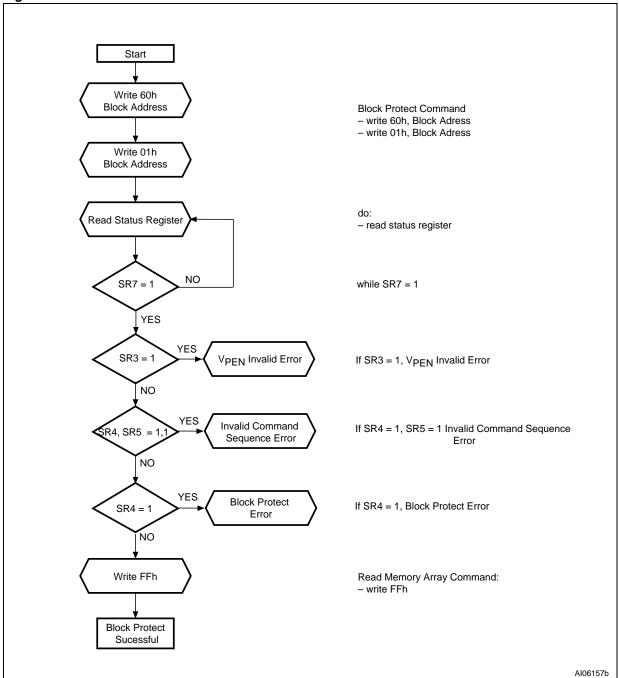

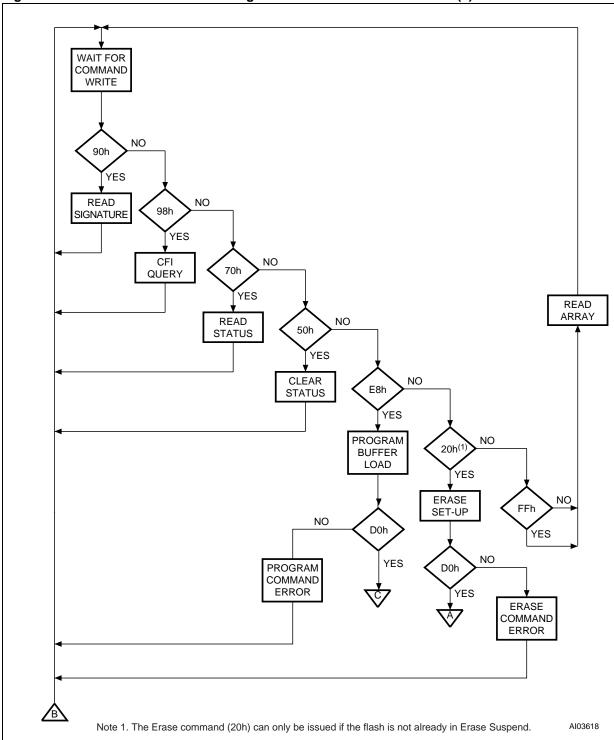

| APPENDIX C. FLOW CHARTS                                                                                                                                                        | 40       |

| Figure 16. Write to Buffer and Program Flowchart and Pseudo Code                                                                                                               | 40       |

| Figure 17. Program Suspend & Resume Flowchart and Pseudo Code                                                                                                                  | 41       |

| Figure 18. Erase Flowchart and Pseudo Code                                                                                                                                     | 42       |

| Figure 19. Erase Suspend & Resume Flowchart and Pseudo Code                                                                                                                    | 43       |

| Figure 20. Block Protect Flowchart and Pseudo Code                                                                                                                             | 44       |

| Figure 21. Block Unprotect Flowchart and Pseudo Code                                                                                                                           | 45       |

| Figure 22. Protection Register Program Flowchart and Pseudo Code                                                                                                               | 46       |

| Figure 23. Command Interface and Program Erase Controller Flowchart (a)                                                                                                        | 47       |

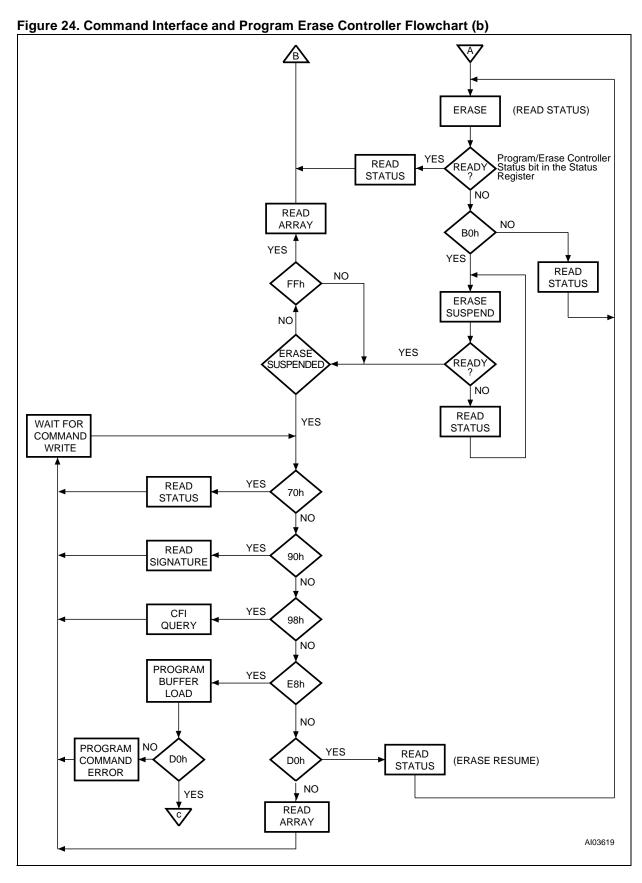

| Figure 24. Command Interface and Program Erase Controller Flowchart (b)                                                                                                        | 48       |

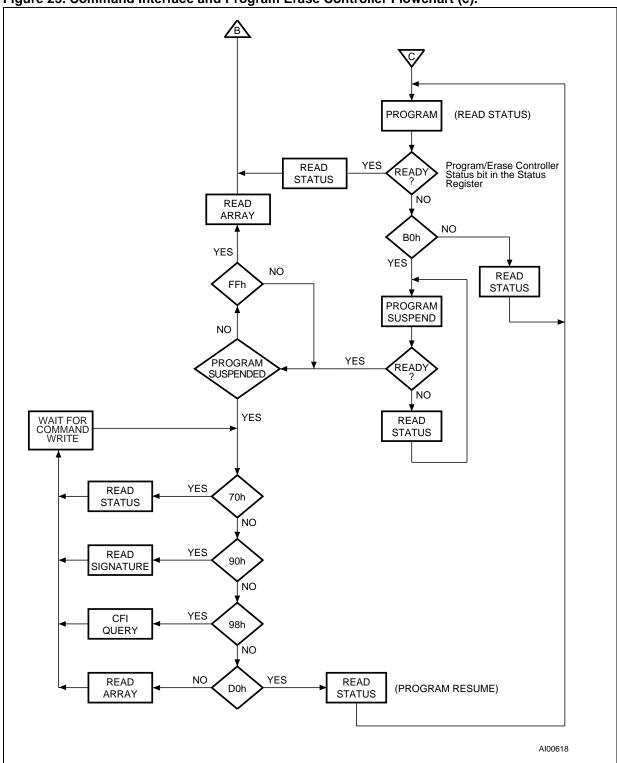

| Figure 25. Command Interface and Program Erase Controller Flowchart (c)                                                                                                        | 49       |

| REVISION HISTORY                                                                                                                                                               | 50       |

| Table 30. Document Revision History                                                                                                                                            | 50       |

#### SUMMARY DESCRIPTION

The M58LW032D is a 32 Mbit (4Mb x 8 or 2Mb x16) non-volatile memory that can be read, erased and reprogrammed. These operations can be performed using a single low voltage (2.7V to 3.6V) core supply.

The memory is divided into 32 blocks of 1Mbit that can be erased independently so it is possible to preserve valid data while old data is erased. Program and Erase commands are written to the Command Interface of the memory. An on-chip Program/Erase Controller simplifies the process of programming or erasing the memory by taking care of all of the special operations that are required to update the memory contents. The end of a Program or Erase operation can be detected and any error conditions identified in the Status Register. The command set required to control the memory is consistent with JEDEC standards.

The Write Buffer allows the microprocessor to program from 1 to 16 Words in parallel, both speeding up the programming and freeing up the microprocessor to perform other work. A Word Program command is available to program a single word.

Erase can be suspended in order to perform either Read or Program in any other block and then resumed. Program can be suspended to Read data in any other block and then resumed. Each block can be programmed and erased over 100,000 cycles.

The M58LW032D has several security features to increase data protection.

Block Protection, where each block can be individually protected against program or erase operations. All blocks are protected during power-up. The protection of the blocks is non-volatile; after power-up the protection status of each block is restored to the state when power was last removed.

- Program Erase Enable input V<sub>PEN</sub>, program or erase operations are not possible when the Program Erase Enable input V<sub>PEN</sub> is low.

- 128 bit Protection Register, divided into two 64 bit segments: the first contains a unique device number written by ST, the second is user programmable. The user programmable segment can be protected.

The Reset/Power-Down pin is used to apply a Hardware Reset to the enabled memory and to set the device in power-down mode.

The device features an Auto Low Power mode. If the bus becomes inactive during read operations, the device automatically enters Auto Low Power mode. In this mode the power consumption is reduced to the Auto Low Power supply current.

The STS signal is an open drain output that can be used to identify the Program/Erase Controller status. It can be configured in two modes: Ready/Busy mode where a static signal indicates the status of the P/E.C, and Status mode where a pulsing signal indicates the end of a Program or Block Erase operation. In Status mode it can be used as a system interrupt signal, useful for saving CPU time

The memory is available in TSOP56 (14 x 20 mm) and TBGA64 (10x13mm, 1mm pitch) packages.

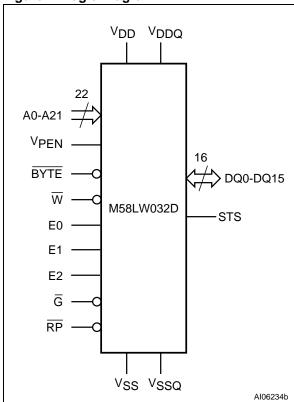

Figure 2. Logic Diagram

**Table 1. Signal Names**

| Table 1. Orginal Names |                                      |  |  |  |  |  |  |  |

|------------------------|--------------------------------------|--|--|--|--|--|--|--|

| A0                     | Address input (used in X8 mode only) |  |  |  |  |  |  |  |

| A1-A21                 | Address inputs                       |  |  |  |  |  |  |  |

| BYTE                   | Byte/Word Organization Select        |  |  |  |  |  |  |  |

| DQ0-DQ15               | Data Inputs/Outputs                  |  |  |  |  |  |  |  |

| E0                     | Chip Enable                          |  |  |  |  |  |  |  |

| E1                     | Chip Enable                          |  |  |  |  |  |  |  |

| E2                     | Chip Enable                          |  |  |  |  |  |  |  |

| G                      | Output Enable                        |  |  |  |  |  |  |  |

| RP                     | Reset/Power-Down                     |  |  |  |  |  |  |  |

| STS                    | Status/(Ready/Busy)                  |  |  |  |  |  |  |  |

| V <sub>PEN</sub>       | Program/Erase Enable                 |  |  |  |  |  |  |  |

| W                      | Write Enable                         |  |  |  |  |  |  |  |

| V <sub>DD</sub>        | Supply Voltage                       |  |  |  |  |  |  |  |

| $V_{DDQ}$              | Input/Output Supply Voltage          |  |  |  |  |  |  |  |

| V <sub>SS</sub>        | Ground                               |  |  |  |  |  |  |  |

| V <sub>SSQ</sub>       | Input/Output Ground                  |  |  |  |  |  |  |  |

| NC                     | Not Connected Internally             |  |  |  |  |  |  |  |

| DU                     | Do Not Use                           |  |  |  |  |  |  |  |

|                        |                                      |  |  |  |  |  |  |  |

Figure 3. TSOP56 Connections

|   | 1      | 2      | 3          | 4                              | 5      | 6                  | 7      | 8                             |

|---|--------|--------|------------|--------------------------------|--------|--------------------|--------|-------------------------------|

| А | (A1)   | A6     | ( A8 )     | V <sub>PEN</sub> ,             | (A13)  | (V <sub>DD</sub> ) | (A18)  | (NC)                          |

| В | (A2)   | (Vss.) | (A9)       | (E0)                           | (A14)  | (DU)               | (A19)  | (E1)                          |

| С | (A3)   | ( A7 ) | (A10)      | (A12)                          | (A15)  | (DU)               | (A20)  | (A21)                         |

| D | (A4)   | ( A5 ) | (A11)      | $\left( \overline{RP} \right)$ | (DU)   | (DU)               | (A16)  | (A17)                         |

| E | (DQ8)  | (DQ1)  | (DQ9)      | (DQ3)                          | DQ4    | (DU)               | (DQ15) | (STS)                         |

| F | (BYTE) | (DQ0)  | (DQ10)     | (DQ11)                         | (DQ12) | (DU)               | (DU)   | $\left( \overline{G} \right)$ |

| G | (NC)   | ( A0 ) | DQ2        | V <sub>DDQ</sub> ,             | DQ5    | DQ6                | (DQ14) | $(\overline{\mathbb{W}})$     |

| Н | ( E2 ) | (DU)   | $(V_{DD})$ | (Vssq.)                        | (DQ13) | (V <sub>SS</sub> ) | (DQ7)  | (NC)                          |

AI06236b

Note: Also see Appendix A, Table 23 for a full listing of the Block Addresses

### SIGNAL DESCRIPTIONS

See Figure 2, Logic Diagram and Table 1, Signal Names, for a brief overview of the signals connected to this device.

**Address Input (A0).** The A0 address input is used to select the higher or lower Byte in X8 mode. It is not used in X16 mode (where A1 is the Lowest Significant bit).

Address Inputs (A1-A21). The Address Inputs are used to select the cells to access in the memory array during Bus Read operations either to read or to program data to. During Bus Write operations they control the commands sent to the Command Interface of the Program/Erase Controller.

The device must be enabled (refer to Table 2, Device Enable) when selecting the addresses. The address inputs are latched on the rising edge of Write Enable or on the first edge of Chip Enables E0, E1 or E2 that disable the device, whichever occurs first.

Data Inputs/Outputs (DQ0-DQ15). The Data Inputs/Outputs output the data stored at the selected address during a Bus Read operation, or are used to input the data during a program operation. During Bus Write operations they represent the commands sent to the Command Interface of the Program/Erase Controller. When used to input data or Write commands they are latched on the rising edge of Write Enable or the first edge of Chip Enables E0, E1 or E2 that disable the device, whichever occurs first.

When the device is enabled and Output Enable is low,  $V_{IL}$  (refer to Table 2, Device Enable), the data bus outputs data from the memory array, the Electronic Signature, the Block Protection status, the CFI Information or the contents of the Status Register. The data bus is high impedance when the device is deselected, Output Enable is high,  $V_{IH}$ , or the Reset/Power-Down signal is low,  $V_{IL}$ . When the Program/Erase Controller is active the Ready/Busy status is given on DQ7.

Chip Enables (E0, E1, E2). The Chip Enable inputs E0, E1 and E2 activate the memory control logic, input buffers, decoders and sense amplifiers. The device is selected at the first edge of Chip Enables E0, E1 or E2 that enable the device and deselected at the first edge of Chip Enables E0, E1 or E2 that disable the device. Refer to Table 2, Device Enable for more details.

When the Chip Enable inputs deselect the memory, power consumption is reduced to the Standby level, I<sub>DD1</sub>.

**Output Enable (G).** The Output Enable,  $\overline{G}$ , gates the outputs through the data output buffers during a read operation. When Output Enable,  $\overline{G}$ , is at  $V_{IH}$  the outputs are high impedance.

Write Enable ( $\overline{\mathbf{W}}$ ). The Write Enable input,  $\overline{\mathbf{W}}$ , controls writing to the Command Interface, Input Address and Data latches. Both addresses and data can be latched on the rising edge of Write Enable.

**Reset/Power-Down (RP).** The Reset/Power-Down pin can be used to apply a Hardware Reset to the memory.

A Hardware Reset is achieved by holding Reset/ Power-Down Low,  $V_{IL}$ , for at least  $t_{PLPH}$ . When Reset/Power-Down is Low,  $V_{IL}$ , the Status Register information is cleared and the power consumption is reduced to power-down level. The device is deselected and outputs are high impedance. If Reset/Power-Down goes low,  $V_{IL}$ ,during a Block Erase, a Write to Buffer and Program or a Block Protect/Unprotect the operation is aborted and the data may be corrupted. In this case the STS pin stays low,  $V_{IL}$ , for a maximum timing of  $t_{PLPH} + t_{PH-BH}$ , until the completion of the Reset/Power-Down pulse.

After Reset/Power-Down goes High,  $V_{IH}$ , the memory will be ready for Bus Read and Bus Write operations after  $t_{PHQV}$ . Note that STS does not fall during a reset, see Ready/Busy Output section.

In an application, it is re<u>com</u>mended to associate Reset/Power-Down pin, RP, with the reset signal of the microprocessor. Otherwise, if a reset operation occurs while the memory is performing an Erase or Program operation, the memory may output the Status Register information instead of being initialized to the default Asynchronous Random Read.

Byte/Word Organization Select (BYTE). The Byte/Word Organization Select pin is used to switch between the x8 and x16 bus widths of the memory. When Byte/Word Organization Select is Low, V<sub>IL</sub>, the memory is in x8 mode, when it is High, V<sub>IH</sub>, the memory is in x16 mode.

**Status/(Ready/Busy) (STS).** The STS signal is an open drain output that can be used to identify the Program/Erase Controller status. It can be configured in two modes:

- Ready/Busy the pin is Low, V<sub>OL</sub>, during Program and Erase operations and high impedance when the memory is ready for any Read, Program or Erase operation.

- Status the pin gives a pulsing signal to indicate the end of a Program or Block Erase operation.

After power-up or reset the STS pin is configured in Ready/Busy mode. The pin can be configured for Status mode using the Configure STS command.

When the Program/Erase Controller is idle, or suspended, STS can float High through a pull-up re-

sistor. The use of an open-drain output allows the STS pins from several memories to be connected to a single pull-up resistor (a Low will indicate that one, or more, of the memories is busy).

STS is not Low during a reset unless the reset was applied when the Program/Erase controller was active.

**Program/Erase Enable (VPEN).** The Program/ Erase Enable input, VPEN, is used to protect all blocks, preventing Program and Erase operations from affecting their data.

Program/Erase Enable must be kept High during all Program/Erase Controller operations, otherwise the operations is not guaranteed to succeed and data may become corrupt.

**V<sub>DD</sub> Supply Voltage.** V<sub>DD</sub> provides the power supply to the internal core of the memory device. It is the main power supply for all operations (Read, Program and Erase).

**V<sub>DDQ</sub> Supply Voltage.** V<sub>DDQ</sub> provides the power supply to the I/O pins and enables all Outputs to be powered independently from V<sub>DD</sub>. V<sub>DDQ</sub> can be tied to V<sub>DD</sub> or can use a separate supply.

It is recommended to power-up and power-down  $V_{DD}$  and  $V_{DDQ}$  together to avoid any condition that would result in data corruption.

**Vss Ground.** Ground, Vss, is the reference for the core power supply. It must be connected to the system ground.

$V_{SSQ}$  Ground.  $V_{SSQ}$  ground is the reference for the input/output circuitry driven by  $V_{DDQ}$ .  $V_{SSQ}$  must be connected to  $V_{SS}$ .

Note: Each device in a system should have  $V_{DD}$  and  $V_{DDQ}$  decoupled with a  $0.1\mu F$  ceramic capacitor close to the pin (high frequency, inherently low inductance capacitors should be as close as possible to the package). See Figure 8, AC Measurement Load Circuit.

**Table 2. Device Enable**

| E2              | E1              | E0              | Device   |

|-----------------|-----------------|-----------------|----------|

| V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | Enabled  |

| V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Disabled |

| V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Disabled |

| V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Disabled |

| V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | Enabled  |

| V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Enabled  |

| V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Enabled  |

| V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Disabled |

Note: For single device operations, E2 and E1 can be connected to  $V_{SS}$ .

#### **BUS OPERATIONS**

There are five standard bus operations that control the memory. Each of these is described in this section, see Tables 3, Bus Operations, for a summary.

On Power-up or after a Hardware Reset the memory defaults to Read Array mode (Page Read).

Typically glitches of less than 5ns on Chip Enable or Write Enable are ignored by the memory and do not affect bus operations.

**Bus Read.** Bus Read operations are used to output the contents of the Memory Array, the Electronic Signature, the Status Register, the Common Flash Interface and the Block Protection Status.

A valid bus operation involves setting the desired address on the Address inputs, enabling the device (refer to Table 2, Device Enable), applying a Low signal,  $V_{IL}$ , to Output Enable and keeping Write Enable High,  $V_{IH}$ . The data read depends on the previous command written to the memory (see Command Interface section).

See Figure 9, Bus Read AC Waveforms, and Table 15, Bus Read AC Characteristics, for details of when the output becomes valid.

**Bus Write.** Bus Write operations write Commands to the memory or latch addresses and input data to be programmed.

A valid Bus Write operation begins by setting the desired address on the Address Inputs and enabling the device (refer to Chip Enable section).

The Address Inputs are latched by the Command Interface on the rising edge of Write Enable or the first edge of E0, E1 or E2 that disables the device (refer to Table 2, Device Enable).

The Data Input/Outputs are latched by the Command Interface on the rising edge of Write Enable or the first edge of E0, E1 or E2 that disables the device whichever occurs first. Output Enable must remain High,  $V_{IH}$ , during the Bus Write operation.

See Figures 11, and 12, Write AC Waveforms, and Tables 17 and 18, Write and Chip Enable Controlled Write AC Characteristics, for details of the timing requirements.

**Output Disable.** The Data Inputs/Outputs are high impedance when the Output Enable is at V<sub>IH</sub>.

**Power-Down.** The memory is <u>in</u> Power-Down mode when Reset/Power-Down, RP, is Low. The power consumption is reduced to the Power-Down level, I<sub>DD2</sub>, and the outputs are high impedance, independent of Chip Enable, Output Enable or Write Enable.

**Standby.** Standby disables most of the internal circuitry, allowing a substantial reduction of the current consumption. The memory is in standby when Chip Enable is at  $V_{IH}$ . The power consumption is reduced to the standby level  $I_{DD1}$  and the outputs are set to high impedance, independently of the Output Enable or Write Enable inputs.

If Chip Enable switches to  $V_{IH}$  during a program or erase operation, the device enters Standby mode when finished.

**Table 3. Bus Operations**

| Bus Operation  | E0, E1<br>or E2 | G               | w               | RP              | A1-A21 (x16)<br>A0-A21 (x8) | DQ0-DQ15 (x16)<br>DQ0-DQ7 (x8) <sup>(1)</sup> |

|----------------|-----------------|-----------------|-----------------|-----------------|-----------------------------|-----------------------------------------------|

| Bus Read       | V <sub>IL</sub> | $V_{IL}$        | V <sub>IH</sub> | V <sub>IH</sub> | Address                     | Data Output                                   |

| Bus Write      | V <sub>IL</sub> | $V_{IH}$        | V <sub>IL</sub> | V <sub>IH</sub> | Address                     | Data Input                                    |

| Output Disable | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Х                           | High Z                                        |

| Power-Down     | Х               | Х               | Х               | V <sub>IL</sub> | Х                           | High Z                                        |

| Standby        | V <sub>IH</sub> | Х               | Х               | V <sub>IH</sub> | Х                           | High Z                                        |

Note: 1. DQ8-DQ15 are High Z in x8 mode.

2.  $X = Don't Care V_{IL} or V_{IH}$ .

#### **READ MODES**

Read operations in the M58LW032D are asynchronous. The device outputs the data corresponding to the address latched, that is the memory array, Status Register, Common Flash Interface, Electronic Signature or Block Protection Status depending on the command issued.

During read operations, if the bus is inactive for a time equivalent to  $t_{\rm AVQV}$ , the device automatically enters Auto Low Power mode. In this mode the internal supply current is reduced to the Auto Low Power supply current,  $t_{\rm IDD5}$ . The Data Inputs/Outputs will still output data if a Bus Read operation is in progress.

Read operations can be performed in two different ways, Random Read (where each Bus Read operation accesses a different Page) and Page Read.

In Page Read mode a Page of data is internally read and stored in a Page Buffer. Each memory page is a 4 Words or 8 Bytes and has the same A3-A21. In x8 mode only A0, A1 and A2 may change, in x16 mode only A1 and A2 may change. The first read operation within the Page has the normal access time ( $t_{AVQV}$ ), subsequent reads within the same Page have much shorter access times ( $t_{AVQV1}$ ). If the Page changes then the normal, longer timings apply again.

See Figure 10, Page Read AC Waveforms and Table 16, Page Read AC Characteristics for details on when the outputs become valid.

#### COMMAND INTERFACE

All Bus Write operations to the memory are interpreted by the Command Interface. Commands consist of one or more sequential Bus Write operations. The Commands are summarized in Table 4, Commands. Refer to Table 4 in conjunction with the text descriptions below.

After power-up or a Reset operation the memory enters Read mode.

Read Memory Array Command. The Read Memory Array command is used to return the memory to Read mode. One Bus Write cycle is required to issue the Read Memory Array command and return the memory to Read mode. Once the command is issued the memory remains in Read mode until another command is issued. From Read mode Bus Read operations will access the memory array. After power-up or a reset the memory defaults to Read Array mode (Page Read).

While the Program/Erase Controller is executing a Program, Erase, Block Protect, Blocks Unprotect or Protection Register Program operation the memory will not accept the Read Memory Array command until the operation completes.

Read Electronic Signature Command. The Read Electronic Signature command is used to read the Manufacturer Code, the Device Code, the Block Protection Status and the Protection Register. One Bus Write cycle is required to issue the Read Electronic Signature command. Once the command is issued subsequent Bus Read operations read the Manufacturer Code, the Device Code, the Block Protection Status or the Protection Register until another command is issued. Refer to Table 6, Read Electronic Signature, Tables 7 and 8, Word and Byte-wide Read Protection Register and Figure 6, Protection Register Memory Map for information on the addresses.

Read Query Command. The Read Query Command is used to read data from the Common Flash Interface (CFI) Memory Area. One Bus Write cycle is required to issue the Read Query Command. Once the command is issued subsequent Bus Read operations read from the Common Flash Interface Memory Area. See Appendix B, Tables 24, 25, 26, 27, 28 and 29 for details on the information contained in the Common Flash Interface (CFI) memory area.

Read Status Register Command. The Read Status Register command is used to read the Status Register. One Bus Write cycle is required to issue the Read Status Register command. Once the command is issued subsequent Bus Read operations read the Status Register until another command is issued.

The Status Register information is present on the output data bus (DQ1-DQ7) when the device is enabled and Output Enable is Low,  $V_{\rm IL}$ .

See the section on the Status Register and Table 10 for details on the definitions of the Status Register bits

Clear Status Register Command. The Clear Status Register command can be used to reset bits SR1, SR3, SR4 and SR5 in the Status Register to '0'. One Bus Write is required to issue the Clear Status Register command.

The bits in the Status Register are sticky and do not automatically return to '0' when a new Write to Buffer and Program, Erase, Block Protect, Block Unprotect or Protection Register Program command is issued. If any error occurs then it is essential to clear any error bits in the Status Register by issuing the Clear Status Register command before attempting a new Program, Erase or Resume command.

**Block Erase Command.** The Block Erase command can be used to erase a block. It sets all of the bits in the block to '1'. All previous data in the block is lost. If the block is protected then the Erase operation will abort, the data in the block will not be changed and the Status Register will output the error.

Two Bus Write operations are required to issue the command; the second Bus Write cycle latches the block address and starts the Program/Erase Controller. Once the command is issued subsequent Bus Read operations read the Status Register. See the section on the Status Register for details on the definitions of the Status Register bits.

During the Erase operation the memory will only accept the Read Status Register command and the Program/Erase Suspend command. All other commands will be ignored. Typical Erase times are given in Table 9.

See Appendix C, Figure 18, Block Erase Flowchart and Pseudo Code, for a suggested flowchart on using the Block Erase command.

Word/Byte Program Command. The Word/Byte Program command is used to program a single Word or Byte in the memory array. Two Bus Write operations are required to issue the command; the first write cycle sets up the Word Program command, the second write cycle latches the address and data to be programmed, and starts the Program/Erase Controller.

If the block being programmed is protected an error will be set in the Status Register and the operation will abort without affecting the data in the memory array. The block must be unprotected using the Blocks Unprotect command or by using the

Blocks Temporary <u>Unprotect</u> feature of the Reset/ Power-Down pin, RP.

Write to Buffer and Program Command. The Write to Buffer and Program command is used to program the memory array.

Up to 16 Words/32 Bytes can be loaded into the Write Buffer and programmed into the memory. Each Write Buffer has the same A5-A21 addresses. In Byte-wide mode only A0-A4 may change in Word-wide mode only A1-A4 may change, in .

Four successive steps are required to issue the command.

- 1. One Bus Write operation is required to set up the Write to Buffer and Program Command. Issue the set up command with the selected memory Block Address where the program operation should occur (any address in the block where the values will be programmed can be used). Any Bus Read operations will start to output the Status Register after the 1st cycle.

- Use one Bus Write operation to write the same block address along with the value N on the Data Inputs/Output, where N+1 is the number of Words/Bytes to be programmed.

- 3. Use N+1 Bus Write operations to load the address and data for each Word into the Write Buffer. See the constraints on the address combinations listed below. The addresses must have the same A5-A21.

- 4. Finally, use one Bus Write operation to issue the final cycle to confirm the command and start the Program operation.

Invalid address combinations or failing to follow the correct sequence of Bus Write cycles will set an error in the Status Register and abort the operation without affecting the data in the memory array. The Status Register should be cleared before re-issuing the command.

If the block being programmed is protected an error will be set in the Status Register and the operation will abort without affecting the data in the memory array. The block must be unprotected using the Blocks Unprotect command.

See Appendix C, Figure 16, Write to Buffer and Program Flowchart and Pseudo Code, for a suggested flowchart on using the Write to Buffer and Program command.

Program/Erase Suspend Command. The Program/Erase Suspend command is used to pause a Word/Byte Program, Write to Buffer and Program or Erase operation. The command will only be accepted during a Program or an Erase operation. It can be issued at any time during an Erase operation but will only be accepted during a Word Program or Write to Buffer and Program command if the Program/Erase Controller is running.

One Bus Write cycle is required to issue the Program/Erase Suspend command and pause the Program/Erase Controller. Once the command is issued it is necessary to poll the Program/Erase Controller Status bit (SR7) to find out when the Program/Erase Controller has paused; no other commands will be accepted until the Program/Erase Controller has paused. After the Program/Erase Controller has paused, the memory will continue to output the Status Register until another command is issued.

During the polling period between issuing the Program/Erase Suspend command and the Program/ Erase Controller pausing it is possible for the operation to complete. Once the Program/Erase Controller Status bit (SR7) indicates that the Program/Erase Controller is no longer active, the Program Suspend Status bit (SR2) or the Erase Suspend Status bit (SR6) can be used to determine if the operation has completed or is suspended. For timing on the delay between issuing the Program/Erase Suspend command and the Program/Erase Controller pausing see Table 9.

During Program/Erase Suspend the Read Memory Array, Read Status Register, Read Electronic Signature, Read Query and Program/Erase Resume commands will be accepted by the Command Interface. Additionally, if the suspended operation was Erase then the Write to Buffer and Program, and the Program Suspend commands will also be accepted. When a program operation is completed inside a Block Erase Suspend the Read Memory Array command must be issued to reset the device in Read mode, then the Erase Resume command can be issued to complete the whole sequence. Only the blocks not being erased may be read or programmed correctly.

See Appendix C, Figure 17, Program Suspend & Resume Flowchart and Pseudo Code, and Figure 19, Erase Suspend & Resume Flowchart and Pseudo Code, for suggested flowcharts on using the Program/Erase Suspend command.

Program/Erase Resume Command. The Program/Erase Resume command can be used to restart the Program/Erase Controller after a Program/Erase Suspend operation has paused it. One Bus Write cycle is required to issue the Program/Erase Resume command. Once the command is issued subsequent Bus Read operations read the Status Register.

Block Protect Command. The Block Protect command is used to protect a block and prevent Program or Erase operations from changing the data in it. Two Bus Write cycles are required to issue the Block Protect command; the second Bus Write cycle latches the block address and starts the Program/Erase Controller. Once the command is issued subsequent Bus Read operations read

the Status Register. See the section on the Status Register for details on the definitions of the Status Register bits.

During the Block Protect operation the memory will only accept the Read Status Register command. All other commands will be ignored. Typical Block Protection times are given in Table 9.

The Block Protection bits are non-volatile, once set they remain set through reset and power-down/power-up. They are cleared by a Blocks Unprotect command.

See Appendix C, Figure 20, Block Protect Flowchart and Pseudo Code, for a suggested flowchart on using the Block Protect command.

Blocks Unprotect Command. The Blocks Unprotect command is used to unprotect all of the blocks. Two Bus Write cycles are required to issue the Blocks Unprotect command; the second Bus Write cycle starts the Program/Erase Controller. Once the command is issued subsequent Bus Read operations read the Status Register. See the section on the Status Register for details on the definitions of the Status Register bits.

During the Block Unprotect operation the memory will only accept the Read Status Register command. All other commands will be ignored. Typical Block Protection times are given in Table 9.

See Appendix C, Figure 21, Block Unprotect Flowchart and Pseudo Code, for a suggested flowchart on using the Block Unprotect command.

Protection Register Program Command. The Protection Register Program command is used to Program the 64 bit user segment of the Protection Register. Two write cycles are required to issue the Protection Register Program command.

- The first bus cycle sets up the Protection Register Program command.

- The second latches the Address and the Data to be written to the Protection Register and starts the Program/Erase Controller.

Read operations output the Status Register content after the programming has started.

The user-programmable segment can be locked by programming bit 1 of the Protection Register Lock location to '0' (see Table 7 and x for Wordwide and Byte-wide protection addressing). Bit 0 of the Protection Register Lock location locks the factory programmed segment and is programmed to '0' in the factory. The locking of the Protection Register is not reversible, once the lock bits are programmed no further changes can be made to the values stored in the Protection Register, see Figure 6, Protection Register Memory Map. Attempting to program a previously protected Protection Register will result in a Status Register error.

The Protection Register Program cannot be suspended. See Appendix C, Figure 22, Protection Register Program Flowchart and Pseudo Code, for the flowchart for using the Protection Register Program command.

# Configure STS Command.

The Configure STS command is used to configure the Status/(Ready/Busy) pin. After power-up or reset the STS pin is configured in Ready/Busy mode. The pin can be configured in Status mode using the Configure STS command (refer to Status/(Ready/Busy) section for more details.

Two write cycles are required to issue the Configure STS command.

- The first bus cycle sets up the Configure STS command.

- The second specifies one of the four possible configurations (refer to Table 5, Configuration Codes):

- Ready/Busy mode

- Pulse on Erase complete mode

- Pulse on Program complete mode

- Pulse on Erase or Program complete mode

The device will not accept the Configure STS command while the Program/Erase controller is busy or during Program/Erase Suspend. When STS pin is pulsing it remains Low for a typical time of 250ns. Any invalid Configuration Code will set an error in the Status Register.

**Table 4. Commands**

|                                | S      | Bus Operations |       |            |       |                    |                    |       |       |       |       |       |      |

|--------------------------------|--------|----------------|-------|------------|-------|--------------------|--------------------|-------|-------|-------|-------|-------|------|

| Command                        | Cycles | 1st Cycle      |       | 2nd Cycle  |       |                    | Subsequent         |       |       | Final |       |       |      |

|                                | 0      | Op.            | Addr. | Data       | Op.   | Addr.              | Data               | Op.   | Addr. | Data  | Op.   | Addr. | Data |

| Read Memory Array              | ≥ 2    | Write          | Х     | FFh        | Read  | RA                 | RD                 |       |       |       |       |       |      |

| Read Electronic Signature      | ≥2     | Write          | Х     | 90h        | Read  | IDA <sup>(2)</sup> | IDD <sup>(2)</sup> |       |       |       |       |       |      |

| Read Status Register           | 2      | Write          | Х     | 70h        | Read  | Х                  | SRD                |       |       |       |       |       |      |

| Read Query                     | ≥2     | Write          | Х     | 98h        | Read  | QA <sup>(3)</sup>  | QD <sup>(3)</sup>  |       |       |       |       |       |      |

| Clear Status Register          | 1      | Write          | Х     | 50h        |       |                    |                    |       |       |       |       |       |      |

| Block Erase                    | 2      | Write          | Х     | 20h        | Write | BA                 | D0                 |       |       |       |       |       |      |

| Word/Byte Program              | 2      | Write          | Х     | 40h<br>10h | Write | PA                 | PD                 |       |       |       |       |       |      |

| Write to Buffer and<br>Program | 4 + N  | Write          | ВА    | E8h        | Write | ВА                 | N                  | Write | PA    | PD    | Write | Х     | D0h  |

| Program/Erase Suspend          | 1      | Write          | Х     | B0h        |       |                    |                    |       |       |       |       |       |      |

| Program/Erase Resume           | 1      | Write          | Х     | D0h        |       |                    |                    |       |       |       |       |       |      |

| Block Protect                  | 2      | Write          | Х     | 60h        | Write | BA                 | 01h                |       |       |       |       |       |      |

| Blocks Unprotect               | 2      | Write          | Х     | 60h        | Write | Х                  | D0h                |       |       |       |       |       |      |

| Protection Register<br>Program | 2      | Write          | Х     | C0h        | Write | PRA                | PRD                |       |       |       |       |       |      |

| Configure STS command          | 2      | Write          | Х     | B8h        | Write | Х                  | CC                 |       |       |       |       |       |      |

Note: 1. X Don't Care; RA Read Address, RD Read Data, IDA Identifier Address, IDD Identifier Data, SRD Status Register Data, PA Program Address; PD Program Data, QA Query Address, QD Query Data, BA Any address in the Block, PRA Protection register address, PRD Protection Register Data, CC Configuration Code.

# **Table 5. Configuration Codes**

| Configuration<br>Code | DQ1 | DQ2 | Mode                                     | STS Pin                                                                      | Description                                                                                                                                  |

|-----------------------|-----|-----|------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 00h                   | 0   | 0   | Ready/Busy                               | V <sub>OL</sub> during P/E<br>operations<br>Hi-Z when the<br>memory is ready | The STS pin is Low during Program and Erase operations and high impedance when the memory is ready for any Read, Program or Erase operation. |

| 01h                   | 0   | 1   | Pulse on Erase complete                  |                                                                              | Supplies a system interrupt pulse at the end of a Block Erase operation.                                                                     |

| 02h                   | 1   | 0   | Pulse on<br>Program<br>complete          | Pulse Low then<br>High when<br>operation                                     | Supplies a system interrupt pulse at the end of a Program operation.                                                                         |

| 03h                   | 1   | 1   | Pulse on Erase<br>or Program<br>complete | completed <sup>(2)</sup>                                                     | Supplies a system interrupt pulse at the end of a Block Erase or Program operation.                                                          |

Note: 1. DQ2-DQ7 are reserved

<sup>2.</sup> For Identifier addresses and data refer to Table 6, Read Electronic Signature.

<sup>3.</sup> For Query Address and Data refer to Appendix B, CFI.

<sup>2.</sup> When STS pin is pulsing it remains Low for a typical time of 250ns.

**Table 6. Read Electronic Signature**

| Code                    | Bus Width | Address (A21-A1) <sup>(3)</sup> | Data (DQ15-DQ0)                                      |  |  |

|-------------------------|-----------|---------------------------------|------------------------------------------------------|--|--|

| Manufacturer Code       | x8        | 000000h                         | 20h                                                  |  |  |

| Manufacturer Code       | x16       | 00000011                        | 0020h                                                |  |  |

| Device Code             | x8        | 000001h                         | 16h                                                  |  |  |

| Device Code             | x16       | 00000111                        | 0016h                                                |  |  |

| Block Protection Status | x8        | SBA <sup>(1)</sup> +02h         | 00h (Block Unprotected)<br>01h (Block Protected)     |  |  |

| Block Protection Status | x16       | ODAY /+UZII                     | 0000h (Block Unprotected)<br>0001h (Block Protected) |  |  |

| Protection Register     | x8, x16   | 000080h <sup>(2)</sup>          | PRD <sup>(1)</sup>                                   |  |  |

Note: 1. SBA is the Start Base Address of each block, PRD is Protection Register Data.

- 2. Base Address, refer to Figure 6 and Tables 7 and 8 for more information.

- 3. A0 is not used in Read Electronic Signature in either x8 or x16 mode. The data is always presented on the lower byte in x16 mode.

Figure 6. Protection Register Memory Map

Table 7. Word-Wide Read Protection Register

| Word | Use                 | A8 | A7 | A6 | A5 | A4 | А3 | A2 | A1 |

|------|---------------------|----|----|----|----|----|----|----|----|

| Lock | Factory, User       | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| 1    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 2    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 3    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 4    | User                | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  |

| 5    | User                | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 0  |

| 6    | User                | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 1  |

| 7    | User                | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

Table 8. Byte-Wide Read Protection Register

| Word | Use                 | A8 | A7 | A6 | A5 | A4 | А3 | A2 | A1 |

|------|---------------------|----|----|----|----|----|----|----|----|

| Lock | Factory, User       | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Lock | Factory, User       | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| 1    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| 2    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 3    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 4    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 5    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 6    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 7    | Factory (Unique ID) | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 8    | User                | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  |

| 9    | User                | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  |

| А    | User                | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 0  |

| В    | User                | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 0  |

| С    | User                | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 1  |

| D    | User                | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 1  |

| E    | User                | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

| F    | User                | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

Table 9. Program, Erase Times and Program Erase Endurance Cycles

| B                                                     |         | M58LW032D            |                    | 1124   |

|-------------------------------------------------------|---------|----------------------|--------------------|--------|

| Parameters                                            | Min     | Typ <sup>(1,2)</sup> | Max <sup>(2)</sup> | Unit   |

| Block (1Mb) Erase                                     |         | 1.2                  | 4.8 <sup>(4)</sup> | s      |

| Chip Program (Write to Buffer)                        |         | 24                   | 72 <sup>(4)</sup>  | s      |

| Chip Erase Time                                       |         | 37                   | 110 <sup>(4)</sup> | s      |

| Program Write Buffer                                  |         | 192 <sup>(3)</sup>   | 576 <sup>(4)</sup> | μs     |

| Word/Byte Program Time<br>(Word/Byte Program command) |         | 16                   | 48 (4)             | μs     |

| Program Suspend Latency Time                          |         | 1                    | 20 <sup>(5)</sup>  | μs     |

| Erase Suspend Latency Time                            |         | 1                    | 25 <sup>(5)</sup>  | μs     |

| Block Protect Time                                    |         | 18                   | 30 <sup>(5)</sup>  | μs     |

| Blocks Unprotect Time                                 |         | 0.75                 | 1.2 <sup>(5)</sup> | s      |

| Program/Erase Cycles (per block)                      | 100,000 |                      |                    | cycles |

| Data Retention                                        | 20      |                      |                    | years  |

Note: 1. Typical values measured at room temperature and nominal voltages.

<sup>2.</sup> Sampled, but not 100% tested.

<sup>3.</sup> Effective byte programming time  $6\mu s$ , effective word programming time  $12\mu s$ .

<sup>4.</sup> Maximum value measured at worst case conditions for both temperature and V<sub>DD</sub> after 100,000 program/erase cycles.

<sup>5.</sup> Maximum value measured at worst case conditions for both temperature and  $V_{DD}$ .

### STATUS REGISTER

The Status Register provides information on the current or previous Program, Erase, Block Protect or Blocks Unprotect operation. The various bits in the Status Register convey information and errors on the operation. They are output on DQ7-DQ0.

To read the Status Register the Read Status Register command can be issued. The Status Register is automatically read after Program, Erase, Block Protect, Blocks Unprotect and Program/Erase Resume commands. The Status Register can be read from any address.

The contents of the Status Register can be updated during an Erase or Program operation by toggling the Output Enable pin or by dis-activating and then reactivating the device (refer to Table 2, Device Enable).

Status Register bits SR5, SR4, SR3 and SR1 are associated with various error conditions and can only be reset with the Clear Status Register command. The Status Register bits are summarized in Table 10, Status Register Bits. Refer to Table 10 in conjunction with the following text descriptions.

**Program/Erase Controller Status (SR7).** The Program/Erase Controller Status bit indicates whether the Program/Erase Controller is active or inactive. When the Program/Erase Controller Status bit is Low,  $V_{OL}$ , the Program/Erase Controller is active and all other Status Register bits are High Impedance; when the bit is High,  $V_{OH}$ , the Program/Erase Controller is inactive.

The Program/Erase Controller Status is Low immediately after a Program/Erase Suspend command is issued until the Program/Erase Controller pauses. After the Program/Erase Controller pauses the bit is High.

During Program, Erase, Block Protect and Blocks Unprotect operations the Program/Erase Controller Status bit can be polled to find the end of the operation. The other bits in the Status Register should not be tested until the Program/Erase Controller completes the operation and the bit is High.

After the Program/Erase Controller completes its operation the Erase Status, Program Status and Block Protection Status bits should be tested for errors.

Erase Suspend Status (SR6). The Erase Suspend Status bit indicates that an Erase operation has been suspended and is waiting to be resumed. The Erase Suspend Status should only be considered valid when the Program/Erase Controller Status bit is High (Program/Erase Controller inactive); after a Program/Erase Suspend command is issued the memory may still complete the operation rather than entering the Suspend mode. When the Erase Suspend Status bit is Low, V<sub>OL</sub>, the Program/Erase Controller is active or has com-

pleted its operation; when the bit is High,  $V_{OH}$ , a Program/Erase Suspend command has been issued and the memory is waiting for a Program/Erase Resume command.

When a Program/Erase Resume command is issued the Erase Suspend Status bit returns Low.

**Erase Status (SR5).** The Erase Status bit can be used to identify if the memory has failed to verify that the block has erased correctly or that all blocks have been unprotected successfully. The Erase Status bit should be read once the Program/Erase Controller Status bit is High (Program/Erase Controller inactive).

When the Erase Status bit is Low,  $V_{OL}$ , the memory has successfully verified that the block has erased correctly or all blocks have been unprotected successfully. When the Erase Status bit is High,  $V_{OH}$ , the erase operation has failed. Depending on the cause of the failure other Status Register bits may also be set to High,  $V_{OH}$ .

- If only the Erase Status bit (SR5) is set High, V<sub>OH</sub>, then the Program/Erase Controller has applied the maximum number of pulses to the block and still failed to verify that the block has erased correctly or that all the blocks have been unprotected successfully.

- If the failure is due to an erase or blocks unprotect with V<sub>PEN</sub> low, V<sub>OL</sub>, then V<sub>PEN</sub> Status bit (SR3) is also set High, V<sub>OH</sub>.

- If the failure is due to an erase on a protected block then Block Protection Status bit (SR1) is also set High, V<sub>OH</sub>.

- If the failure is due to a program or erase incorrect command sequence then Program Status bit (SR4) is also set High, V<sub>OH</sub>.

Once set High, the Erase Status bit can only be reset Low by a Clear Status Register command or a hardware reset. If set High it should be reset before a new Program or Erase command is issued, otherwise the new command will appear to fail.

**Program Status (SR4).** The Program Status bit is used to identify a Program or Block Protect failure. The Program Status bit should be read once the Program/Erase Controller Status bit is High (Program/Erase Controller inactive).

When the Program Status bit is Low,  $V_{OL}$ , the memory has successfully verified that the Write Buffer has programmed correctly or the block is protected. When the Program Status bit is High,  $V_{OH}$ , the program or block protect operation has failed. Depending on the cause of the failure other Status Register bits may also be set to High,  $V_{OH}$ .

If only the Program Status bit (SR4) is set High, V<sub>OH</sub>, then the Program/Erase Controller has applied the maximum number of pulses to the byte and still failed to verify that the Write Buffer has programmed correctly or that the Block is protected.

- If the failure is due to a program or block protect with V<sub>PEN</sub> low, V<sub>OL</sub>, then V<sub>PEN</sub> Status bit (SR3) is also set High, V<sub>OH</sub>.

- If the failure is due to a program on a protected block then Block Protection Status bit (SR1) is also set High, V<sub>OH</sub>.

- If the failure is due to a program or erase incorrect command sequence then Erase Status bit (SR5) is also set High, V<sub>OH</sub>.

Once set High, the Program Status bit can only be reset Low by a Clear Status Register command or a hardware reset. If set High it should be reset before a new Program or Erase command is issued, otherwise the new command will appear to fail.

**V<sub>PEN</sub> Status (SR3).** The V<sub>PEN</sub> Status bit can be used to identify if a Program, Erase, Block Protection or Block Unprotection operation has been attempted when V<sub>PEN</sub> is Low, V<sub>IL</sub>.

When the  $V_{PEN}$  Status bit is Low,  $V_{OL}$ , no Program, Erase, Block Protection or Block Unprotection operations have been attempted with  $V_{PEN}$  Low,  $V_{IL}$ , since the last Clear Status Register command, or hardware reset. When the  $V_{PEN}$  Status bit is High,  $V_{OH}$ , a Program, Erase, Block Protection or Block Unprotection operation has been attempted with  $V_{PEN}$  Low,  $V_{IL}$ .

Once set High, the V<sub>PEN</sub> Status bit can only be reset by a Clear Status Register command or a hardware reset. If set High it should be reset before a new Program, Erase, Block Protection or Block Unprotection command is issued, otherwise the new command will appear to fail.

**Program Suspend Status (SR2).** The Program Suspend Status bit indicates that a Program oper-

ation has been suspended and is waiting to be resumed. The Program Suspend Status should only be considered valid when the Program/Erase Controller Status bit is High (Program/Erase Controller inactive); after a Program/Erase Suspend command is issued the memory may still complete the operation rather than entering the Suspend mode.

When the Program Suspend Status bit is Low,  $V_{OL}$ , the Program/Erase Controller is active or has completed its operation; when the bit is High,  $V_{OH}$ , a Program/Erase Suspend command has been issued and the memory is waiting for a Program/Erase Resume command.

When a Program/Erase Resume command is issued the Program Suspend Status bit returns Low.

**Block Protection Status (SR1).** The Block Protection Status bit can be used to identify if a Program or Erase operation has tried to modify the contents of a protected block.

When the Block Protection Status bit is Low,  $V_{OL}$ , no Program or Erase operations have been attempted to protected blocks since the last Clear Status Register command or hardware reset; when the Block Protection Status bit is High,  $V_{OH}$ , a Program (Program Status bit SR4 set High) or Erase (Erase Status bit SR5 set High) operation has been attempted on a protected block.

Once set High, the Block Protection Status bit can only be reset Low by a Clear Status Register command or a hardware reset. If set High it should be reset before a new Program or Erase command is issued, otherwise the new command will appear to fail.

**Reserved (SR0).** Bit SR0 of the Status Register is reserved. Its value should be masked.

**Table 10. Status Register Bits**

| OPERATION                                                          | SR7 | SR6 | SR5  | SR4 | SR3 | SR2 | SR1 | Result<br>(Hex) |

|--------------------------------------------------------------------|-----|-----|------|-----|-----|-----|-----|-----------------|

| Program/Erase Controller active                                    | 0   |     | Hi-Z |     |     |     |     | N/A             |

| Write Buffer not ready                                             | 0   |     | Hi-Z |     |     |     |     | N/A             |

| Write Buffer ready                                                 | 1   | 0   | 0    | 0   | 0   | 0   | 0   | 80h             |

| Write Buffer ready in Erase Suspend                                | 1   | 1   | 0    | 0   | 0   | 0   | 0   | C0h             |

| Program suspended                                                  | 1   | 0   | 0    | 0   | 0   | 1   | 0   | 84h             |

| Program suspended in Erase Suspend                                 | 1   | 1   | 0    | 0   | 0   | 1   | 0   | C4h             |

| Program/Block Protect completed successfully                       | 1   | 0   | 0    | 0   | 0   | 0   | 0   | 80h             |

| Program completed successfully in Erase Suspend                    | 1   | 1   | 0    | 0   | 0   | 0   | 0   | C0h             |

| Program/Block protect failure due to incorrect command sequence    | 1   | 0   | 1    | 1   | 0   | 0   | 0   | B0h             |

| Program failure due to incorrect command sequence in Erase Suspend | 1   | 1   | 1    | 1   | 0   | 0   | 0   | F0h             |

| Program/Block Protect failure due to VPEN error                    | 1   | 0   | 0    | 1   | 1   | 0   | 0   | 98h             |

| Program failure due to V <sub>PEN</sub> error in Erase Suspend     | 1   | 1   | 0    | 1   | 1   | 0   | 0   | D8h             |

| Program failure due to Block Protection                            | 1   | 0   | 0    | 1   | 0   | 0   | 1   | 92h             |

| Program failure due to Block Protection in Erase Suspend           | 1   | 1   | 0    | 1   | 0   | 0   | 1   | D2h             |

| Program/Block Protect failure due to cell failure                  | 1   | 0   | 0    | 1   | 0   | 0   | 0   | 90h             |

| Program failure due to cell failure in Erase<br>Suspend            | 1   | 1   | 0    | 1   | 0   | 0   | 0   | D0h             |

| Erase Suspended                                                    | 1   | 1   | 0    | 0   | 0   | 0   | 0   | C0h             |

| Erase/Blocks Unprotect completed successfully                      | 1   | 0   | 0    | 0   | 0   | 0   | 0   | 80h             |

| Erase/Blocks Unprotect failure due to incorrect command sequence   | 1   | 0   | 1    | 1   | 0   | 0   | 0   | B0h             |

| Erase/Blocks Unprotect failure due to VPEN error                   | 1   | 0   | 1    | 0   | 1   | 0   | 0   | A8h             |

| Erase failure due to Block Protection                              | 1   | 0   | 1    | 0   | 0   | 0   | 1   | A2h             |

| Erase/Blocks Unprotect failure due to failed cells in Block        |     | 0   | 1    | 0   | 0   | 0   | 0   | A0h             |

| Configure STS error due to invalid configuration code              | 1   | 0   | 1    | 1   | 0   | 0   | 0   | B0h             |

## **MAXIMUM RATING**

Stressing the device above the ratings listed in Table 11, Absolute Maximum Ratings, may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is

not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

**Table 11. Absolute Maximum Ratings**

| Symbol                             | Parameter                    | Va          | Unit                  |       |

|------------------------------------|------------------------------|-------------|-----------------------|-------|

| Symbol                             | ratameter                    | Min         | Max                   | Oilit |

| T <sub>BIAS</sub>                  | Temperature Under Bias       | -40         | 125                   | °C    |

| T <sub>STG</sub>                   | Storage Temperature          | <b>-</b> 55 | 150                   | °C    |

| V <sub>IO</sub>                    | Input or Output Voltage      | -0.6        | V <sub>DDQ</sub> +0.6 | V     |

| V <sub>DD</sub> , V <sub>DDQ</sub> | Supply Voltage               | -0.6        | 5.0                   | V     |

| losc                               | Output Short-circuit Current |             | 100 <sup>(1)</sup>    | mA    |

Note: 1. Maximum one output short-circuited at a time and for no longer than 1 second.

## DC AND AC PARAMETERS

This section summarizes the operating and measurement conditions, and the DC and AC characteristics of the device. The parameters in the DC and AC characteristics Tables that follow, are derived from tests performed under the Measure-

ment Conditions summarized in Table 12, Operating and AC Measurement Conditions. Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parameters.

**Table 12. Operating and AC Measurement Conditions**

| Parameter                                       | M58LV                 | Units |                  |    |

|-------------------------------------------------|-----------------------|-------|------------------|----|

| raiametei                                       | Min                   | Max   | Offics           |    |

| Supply Voltage (V <sub>DD</sub> )               | 2.7                   | 3.6   | V                |    |

| Input/Output Supply Voltage (V <sub>DDQ</sub> ) | 2.7                   | 3.6   | V                |    |

| Ambient Temperature (T <sub>A</sub> )           | Grade 1               | 0     | 70               | °C |

| Ambient remperature (14)                        | Grade 6               | -40   | 85               | °C |

| Load Capacitance (C <sub>L</sub> )              |                       | 30    |                  | pF |

| Input Pulses Voltages                           | 0 to V <sub>DDQ</sub> |       | V                |    |

| Input and Output Timing Ref. Voltages           |                       | 0.5 \ | / <sub>DDQ</sub> | V  |

Figure 7. AC Measurement Input Output Waveform

Figure 8. AC Measurement Load Circuit

Table 13. Capacitance

| Symbol           | Parameter          | Test Condition        | Тур | Max | Unit |

|------------------|--------------------|-----------------------|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = 0V  | 6   | 8   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V | 8   | 12  | pF   |

Note: 1.  $T_A = 25^{\circ}C$ , f = 1 MHz

<sup>2.</sup> Sampled only, not 100% tested.

**Table 14. DC Characteristics**

| Symbol            | Parameter                                                                | Test Condition                                   | Min                   | Max                    | Unit |

|-------------------|--------------------------------------------------------------------------|--------------------------------------------------|-----------------------|------------------------|------|

| ILI               | Input Leakage Current                                                    | $0V \le V_{IN} \le V_{DDQ}$                      |                       | ±1                     | μΑ   |

| I <sub>LO</sub>   | Output Leakage Current                                                   | $0V \le V_{OUT} \le V_{DDQ}$                     |                       | ±5                     | μΑ   |

| I <sub>DD</sub>   | Supply Current (Random Read)                                             | $\overline{E} = V_{IL}$ , f=5MHz                 |                       | 20                     | mA   |

| I <sub>DDO</sub>  | Supply Current (Page Read)                                               | $\overline{E} = V_{IL}$ , f=33MHz                |                       | 29                     | mA   |

| I <sub>DD1</sub>  | Supply Current (Standby)                                                 | $\overline{E} = V_{IH},  \overline{RP} = V_{IH}$ |                       | 40                     | μΑ   |

| I <sub>DD5</sub>  | Supply Current (Auto Low-Power)                                          | $\overline{E} = V_{IL}, \overline{RP} = V_{IH}$  |                       | 40                     | μΑ   |

| I <sub>DD2</sub>  | Supply Current (Reset/Power-Down)                                        | RP = V <sub>IL</sub>                             |                       | 40                     | μA   |

| I <sub>DD3</sub>  | Supply Current (Program or Erase,<br>Block Protect, Block Unprotect)     | Program or Erase operation in progress           |                       | 30                     | mA   |

| I <sub>DD4</sub>  | Supply Current<br>(Erase/Program Suspend)                                | E = V <sub>IH</sub>                              |                       | 40                     | μΑ   |

| VIL               | Input Low Voltage                                                        |                                                  | -0.5                  | 0.8                    | V    |

| V <sub>IH</sub>   | Input High Voltage                                                       |                                                  | 2                     | V <sub>DDQ</sub> + 0.5 | V    |

| Vol               | Output Low Voltage                                                       | I <sub>OL</sub> = 100μA                          |                       | 0.2                    | V    |

| V <sub>OH</sub>   | Output High Voltage                                                      | I <sub>OH</sub> = -100μA                         | V <sub>DDQ</sub> -0.2 |                        | V    |

| V <sub>LKO</sub>  | V <sub>DD</sub> Supply Voltage (Erase and Program lockout)               |                                                  | 2                     |                        | V    |

| V <sub>PENH</sub> | V <sub>PEN</sub> Supply Voltage (block erase, program and block protect) |                                                  | 2.7                   | 3.6                    | V    |

Figure 9. Bus Read AC Waveforms

Note: 1. V<sub>IH</sub> = Device Disabled (first edge of E0, E1 or E2), V<sub>IL</sub> = Device Enabled (first edge of E0, E1 or E2). Refer to Table 2 for more details.

2. BYTE can be Low or High.

Table 15. Bus Read AC Characteristics.